# CY93C01/02/04/08/16

# 1 Kbit, 2 Kbit, 4 Kbit, 8 Kbit, and 16 Kbit (x8 or x16) MicroWire Serial EEPROM

## Features

- Continuous voltage operation  $\Box V_{CC} = 1.65V$  to 5.5V

- Internally organized as x8 or x16

- Industry standard three wire serial interface

- Schmitt trigger, filtered inputs for noise suppression

- Programming instructions that work on byte, word, or entire memory

- Sequential read operation

- 4 MHz clock rate (5V) compatibility

- Self timed write cycle (5 ms max)

- Ready/Busy signal during programming

- Industrial temperature range

- High reliability

Endurance: 1 million write cycles

Data retention: 100 years

- RoHS compliant 8-Pin SOIC and 8-Pin TSSOP packages

- Pb-free and RoHS compliant

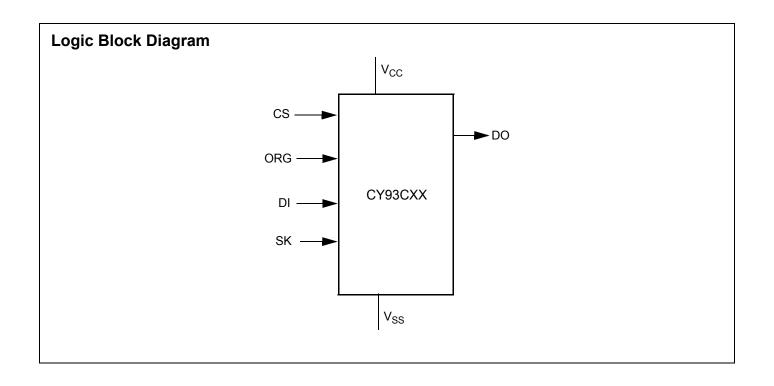

## **Functional Description**

The CY93C01/02/04/08/16 provides 1K, 2K, 4K, 8K, and 16K bits of serial Electrically Erasable and Programmable Read Only Memory (EEPROM). The memory is organized as x16 when the ORG pin is connected to V<sub>CC</sub> and as x8 when it is tied to ground. The device is optimized for use in many industrial applications, where low power and low voltage operations are essential. The CY93C01/02/04/08/16 is available in space saving 8-Pin SOIC, and 8-Pin TSSOP packages. The CY93C01/02/04/08/16 is enabled through the Chip Select pin (CS), and accessed through a three wire serial interface consisting of Data Input (DI), Data Output (DO), and Serial Clock (SK). On receiving a read instruction at DI, the address is decoded and the data is clocked out serially on the data output pin DO. The write cycle is completely self timed and no separate erase cycle is required before write. The write cycle is enabled only when the part is in the erase or write enable state. When CS is brought high following the initiation of a write cycle, the DO pin outputs the Ready/Busy status of the part. The CY93C01/02/04/08/16 is available in a 1.65V to 5.5V version.

198 Champion Court

San Jose, CA 95134-1709 • 408-943-2600 Revised February 05, 2009

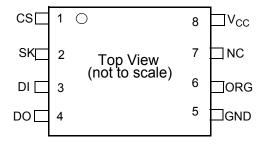

## **Pinouts**

## Figure 1. Pin Diagram: 8-Pin SOIC/TSSOP Package

## Table 1. Pin Definition - 8-SOIC/TSSOP

| Pin Name        | 8-SOIC<br>Pin Number | 8-TSSOP<br>Pin Number | I/О Туре | Description                          |

|-----------------|----------------------|-----------------------|----------|--------------------------------------|

| CS              | 1                    | 1                     | Input    | Chip Select                          |

| SK              | 2                    | 2                     | Input    | Serial Clock                         |

| DI              | 3                    | 3                     | Input    | Serial Data Input                    |

| DO              | 4                    | 4                     | Output   | Serial Data Output                   |

| GND             | 5                    | 5                     | Input    | Ground                               |

| ORG             | 6                    | 6                     | Input    | Internal Organization <sup>[1]</sup> |

| NC              | 7                    | 7                     | NA       | No Connect <sup>[2]</sup>            |

| V <sub>CC</sub> | 8                    | 8                     | Input    | Power Supply                         |

Notes

The NC pin does not contribute to the normal operation of the device. The pin may be left unconnected or may be connected to Vcc or GND. Direct connection of NC to GND is recommended for lowest standby power consumption.

<sup>1.</sup> When the ORG is connected to Vcc, the x16 organization is selected. When it is connected to ground, the x8 organization is selected. If the ORG pin is left unconnected and the application does not load the input beyond the capability of the internal 1Meg ohm pull up, then the x16 organization is selected.

## **Device Operating Features**

#### **Internal Device Reset**

To prevent inadvertent write operations during power up, a Power On Reset (POR) circuit is included.

During power up and power down, the device must not be selected (that is, the Chip Select Input (CS) must be driven low) until the supply voltage reaches the operating voltage  $V_{CC}$ .

During power up (the phase during which V<sub>CC</sub> is lower than the minimum V<sub>CC</sub>, but increases continuously), the device does not respond to any instruction until V<sub>CC</sub> has reached the POR threshold voltage (this threshold is lower than the minimum V<sub>CC</sub> operating voltage defined in DC Electrical Characteristics on page 9). After V<sub>CC</sub> has passed the POR threshold, the device is reset.

Before selecting the memory and issuing instructions to it, a valid and stable  $V_{CC}$  voltage is applied. This voltage must remain stable and valid until the end of transmission of the instruction and, for a write instruction, until the completion of the internal write cycle (t<sub>WC</sub>).

During power down (the phase during which  $V_{CC}$  decreases continuously), as soon as  $V_{CC}$  drops from the normal operating voltage below the POR threshold voltage, the device stops responding to any instruction sent to it.

#### Active and Standby Power Modes

When Chip Select (CS) is high, the device is selected and in the active power mode. It consumes  $I_{CC}$ , as specified in DC Electrical Characteristics on page 9. When Chip Select (CS) is low, the device is deselected.

If no erase or write cycle is in progress when Chip Select goes low, the device enters the standby power mode and the power consumption drops to  $I_{SB1}$ .

## **Device Operations**

The CY93C02 is accessed through a simple and versatile three wire serial communication interface. Device operation is controlled by seven instructions issued by the host processor. A valid instruction starts with a rising edge of CS and consists of a Start Bit (logic '1') followed by the appropriate op-code and the desired memory address location.

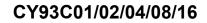

#### Read

The Read (READ) instruction contains the address code for the memory location to be read. After the instruction and address are decoded, data from the selected memory location is available at the serial output pin DO. Output data changes are synchronized with the rising edges of serial clock SK. Note that a dummy bit (logic '0') precedes the 8-bit or 16-bit data output string. The CY93C02 supports sequential read operations. The device automatically increments the internal address pointer and clocks out the next memory location as long as CS is held high. In this case, the dummy bit (logic '0') is not clocked out between memory locations, therefore enabling a continuous stream of data to be read.

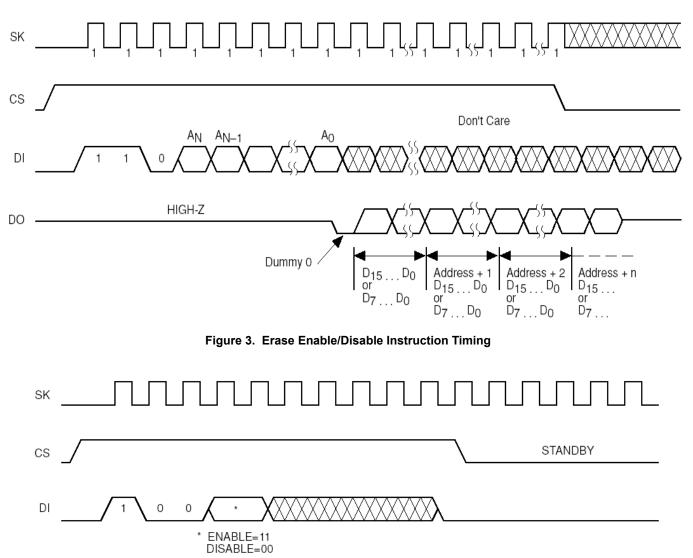

#### Write

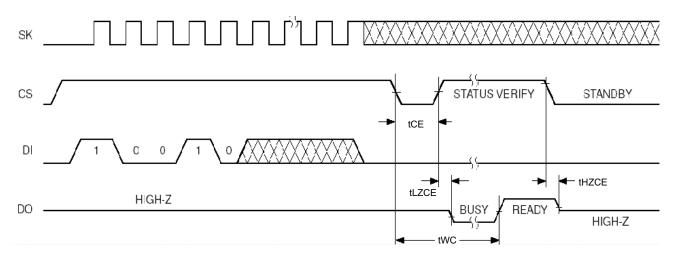

The Write (WRITE) instruction contains 8 or 16 bits of data to be written into the specified memory location. The self timed programming cycle  $t_{WC}$  starts after the last bit of data is rec<u>eived</u> at serial data input pin DI. The DO pin outputs the Ready/Busy status of the part if CS is brought high after being kept low for a minimum of 100 ns ( $t_{CE}$ ). A logic '0' at DO indicates that programming is still in progress. A logic '1' indicates that the memory location at the specified address is written with the data pattern contained in the instruction and the part is ready for further instructions. A Ready/Busy status is not obtained if the CS is brought high after the end of the self timed programming cycle  $t_{WC}$ .

An internal power on data protection mechanism in the CY93C02 inhibits the device when the supply is too low.

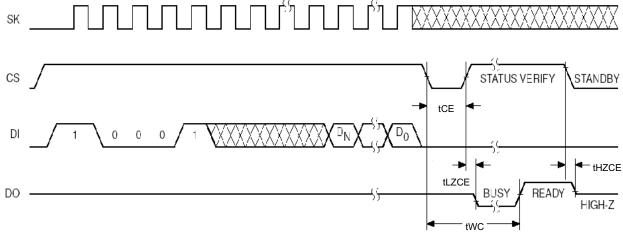

#### Erase

The Erase (ERASE) instruction programs all bits in the specified memory location to the logical '1' state. The self timed erase cycle starts after the ERASE instruction and address are decoded. The DO pin outputs the Ready/Busy status of the part if CS is brought high after being kept low for a minimum of 100 ns ( $t_{CE}$ ). A logic '1' at pin DO indicates that the selected memory location is erased, and the part is ready for another instruction.

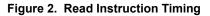

## Erase/Write Enable (EWEN)

To assure data integrity, the part automatically goes into the Erase/Write Disable (EWDS) state when power is first applied. An Erase/Write Enable (EWEN) instruction must be executed first before any programming instruction is carried out. Note that in the EWEN state, programming remains enabled until an EWDS instruction is executed or V<sub>CC</sub> power is removed from the part.

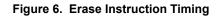

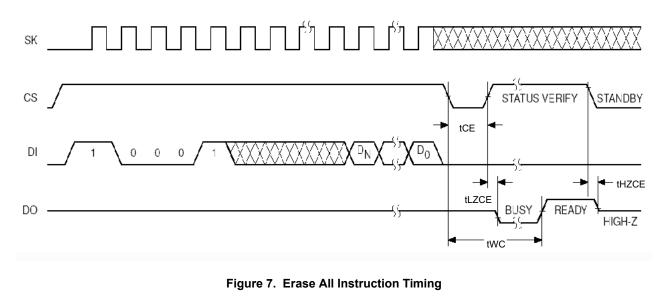

#### Erase All (ERAL)

The Erase All (ERAL) instruction programs every bit in the memory array to the logic '1' state and is prim<u>arily</u> used for testing purposes. The DO pin outputs the Ready/Busy status of the part if CS is brought high after being kept low for a minimum of 100 ns ( $t_{CE}$ ).

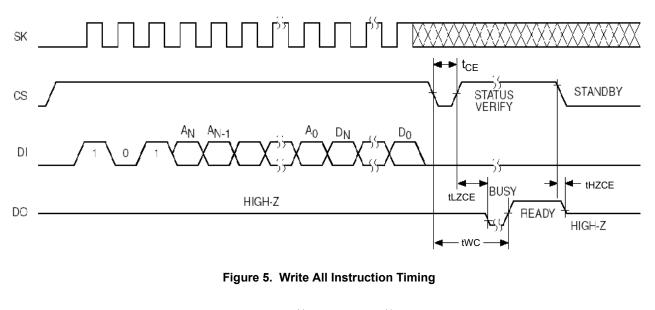

## Write All (WRAL)

The Write All (WRAL) instruction programs all memory locations with the data patterns specified in the instruction. The DO pin outputs the Ready/Busy status of the part if CS is brought high after being kept low for a minimum of 100 ns ( $t_{CE}$ ).

#### Erase/Write Disable (EWDS)

To protect against accidental data disturbance, the Erase/Write Disable (EWDS) instruction disables all programming modes and is executed after all programming operations. The operation of the READ instruction is independent of both the EWEN and EWDS instructions and is executed at any time.

# Table 2. Instruction Set for CY93C01 <sup>[3]</sup>

| Instruction | Start Bit | Opcode | Add     | ress   | Data  |        | Comments            |

|-------------|-----------|--------|---------|--------|-------|--------|---------------------|

| matuction   | otart Dit | Opcode | x8      | x16    | x8    | x16    | oonmenta            |

| READ        | 1         | 10     | A6–A0   | A5–A0  |       |        | Read Address AN–A0  |

| ERASE       | 1         | 11     | A6–A0   | A5–A0  |       |        | Clear Address AN–A0 |

| WRITE       | 1         | 01     | A6–A0   | A5–A0  | D7–D0 | D15–D0 | Write Address AN–A0 |

| EWEN        | 1         | 00     | 11XXXXX | 11XXXX |       |        | Write Enable        |

| EWDS        | 1         | 00     | 00XXXXX | 00XXXX |       |        | Write Disable       |

| ERAL        | 1         | 00     | 10XXXXX | 10XXXX |       |        | Clear All Address   |

| WRAL        | 1         | 00     | 01XXXXX | 01XXXX | D7–D0 | D15–D0 | Write All Address   |

## Table 3. Instruction Set for CY93C02 and CY93C04 <sup>[3]</sup>

| Instruction | Start Bit | Opcode | Add                   | ress                  | Data  |        | Comments            |

|-------------|-----------|--------|-----------------------|-----------------------|-------|--------|---------------------|

| mstruction  | Start Dit | Opcode | x8                    | x16                   | x8    | x16    | Comments            |

| READ        | 1         | 10     | A8 <sup>[4]</sup> –A0 | A7 <sup>[5]</sup> –A0 |       |        | Read Address AN–A0  |

| ERASE       | 1         | 11     | A8 <sup>[4]</sup> –A0 | A7 <sup>[5]</sup> –A0 |       |        | Clear Address AN–A0 |

| WRITE       | 1         | 01     | A8 <sup>[4]</sup> –A0 | A7 <sup>[5]</sup> –A0 | D7–D0 | D15–D0 | Write Address AN–A0 |

| EWEN        | 1         | 00     | 11XXXXXXX             | 11XXXXXX              |       |        | Write Enable        |

| EWDS        | 1         | 00     | 00XXXXXXX             | 00XXXXXX              |       |        | Write Disable       |

| ERAL        | 1         | 00     | 10XXXXXXX             | 10XXXXXX              |       |        | Clear All Address   |

| WRAL        | 1         | 00     | 01XXXXXXX             | 01XXXXXX              | D7-D0 | D15–D0 | Write All Address   |

#### Table 4. Instruction Set for CY93C08 and CY93C16<sup>[3]</sup>

| Instruction | Start Bit | Opcode | Add                    | ress                  | Data  |        | Comments            |

|-------------|-----------|--------|------------------------|-----------------------|-------|--------|---------------------|

| instruction | Start Dit | Opcode | x8                     | x16                   | x8    | x16    | Comments            |

| READ        | 1         | 10     | A10 <sup>[6]</sup> –A0 | A9 <sup>[7]</sup> –A0 |       |        | Read Address AN–A0  |

| ERASE       | 1         | 11     | A10 <sup>[6]</sup> –A0 | A9 <sup>[7]</sup> –A0 |       |        | Clear Address AN–A0 |

| WRITE       | 1         | 01     | A10 <sup>[6]</sup> –A0 | A9 <sup>[7]</sup> –A0 | D7–D0 | D15–D0 | Write Address AN–A0 |

| EWEN        | 1         | 00     | 11XXXXXXXXX            | 11XXXXXXXX            |       |        | Write Enable        |

| EWDS        | 1         | 00     | 00XXXXXXXX             | 00XXXXXXXX            |       |        | Write Disable       |

| ERAL        | 1         | 00     | 10XXXXXXXXX            | 10XXXXXXXX            |       |        | Clear All Address   |

| WRAL        | 1         | 00     | 01XXXXXXXXX            | 01XXXXXXXX            | D7–D0 | D15–D0 | Write All Address   |

#### Notes

- X = Do not care bit.

Address bit A8 is not decoded by CY93C02.

Address bit A7 is not decoded by CY93C02.

Address bit A10 is not decoded by CY93C08.

Address bit A9 is not decoded by CY93C08.

# Ready/Busy Status

While the Write or Erase cycle is underway, for a WRITE, ERASE, WRAL or ERAL instruction, the Busy signal (DO=0) is returned whenever Chip Select input (CS) is driven high. In this state, the CY93C02 ignores any data on the bus. When the write cycle is completed, and Chip Select input (CS) is driven high, the Ready signal (DO=1) indicates that the CY93C02 is ready to receive the next instruction. Serial Data Output (DO) remains set to 1 until the Chip Select Input (CS) is brought low or until a new start bit is decoded.

## Common I/O Operation

Serial Data Output (DO) and Serial Data Input (DI) are connected together, through a current limiting resistor, to form a common, single wire data bus. Some precautions must be taken when operating the memory in this way, mostly to prevent a short circuit current from flowing when the last address bit (A0) clashes with the first data bit on Serial Data Output (DO).

## **Clock Pulse Counter**

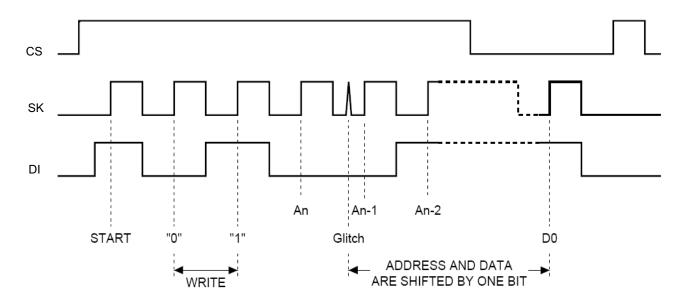

In a noisy environment, the number of pulses received on Serial Clock (SK) may be greater than the number delivered by the master (the microcontroller). This leads to a misalignment of the instruction of one or more bits, as shown in Figure 8 on page 8, and may lead to the writing of erroneous data at an erroneous address. To combat this problem, the CY93C02 has an on-chip counter that counts the clock pulses from the start bit until the falling edge of the Chip Select input (CS). If the number of clock pulses received is not the number expected, the WRITE, ERASE, ERAL, or WRAL instruction is aborted and the contents of the memory are not modified.

Page 5 of 16

Figure 8. Write Sequence with One Clock Glitch

# **Maximum Ratings**

Exceeding maximum ratings may impair the useful life of the device. These user guidelines are not tested.

| Storage temperature65°C to +150°C                                                |

|----------------------------------------------------------------------------------|

| Ambient temperature with power applied–55°C to +125°C                            |

| Supply voltage on $V_{CC}$ relative to GND1.0V to +6.0V                          |

| DC voltage applied to outputs in high-Z state–0.5V to $V_{CC}$ + 1.0V            |

| Input voltage –0.5V to $V_{CC}$ + 0.5V                                           |

| Transient voltage (<20 ns) on any pin to ground potential1.0V to $V_{CC}$ + 2.0V |

| Package power dissipation<br>capability (T <sub>A</sub> = 25°C) | 1.0W                  |

|-----------------------------------------------------------------|-----------------------|

| Surface mount lead soldering<br>Temperature (3 Seconds)         | +260°C for 10 seconds |

| Output short circuit current <sup>[8]</sup>                     | 50 mA                 |

| Static discharge voltage<br>(per MIL-STD-883, Method 3015)      | > 2001V               |

| Latch up current                                                | > 200 mA              |

## **Operating Range**

| Range      | Ambient Temperature | V <sub>cc</sub> |

|------------|---------------------|-----------------|

| Industrial | –40°C to +85°C      | 1.65V to 5.5V   |

# **DC Electrical Characteristics**

Over the Operating Range ( $V_{CC}$  = 1.65V to 5.5V)

| Parameter        | Description            | Test Conditions                                                              | Min                   | Max                                  | Unit |

|------------------|------------------------|------------------------------------------------------------------------------|-----------------------|--------------------------------------|------|

| V <sub>CC1</sub> | Supply Voltage         |                                                                              | 1.65                  | 5.5                                  | V    |

| I <sub>SB1</sub> | Standby Current        | $V_{CC}$ = 1.65V, $\overline{CS}$ = $V_{CC}$                                 |                       | 1                                    | μA   |

| I <sub>SB2</sub> | Standby Current        | $V_{CC} = 2.7V, \overline{CS} = V_{CC}$                                      |                       | 1.1                                  | μA   |

| I <sub>SB3</sub> | Standby Current        | $V_{CC} = 5.5V, \overline{CS} = V_{CC}$                                      |                       | 1.2                                  | μA   |

| I <sub>CC1</sub> | Supply Current (Read)  | V <sub>CC</sub> = 5.5V at 4 MHz                                              |                       | 2                                    | mA   |

| I <sub>CC2</sub> | Supply Current (Write) | V <sub>CC</sub> = 5.5V                                                       |                       | 2                                    | mA   |

| I <sub>LI</sub>  | Input Leakage Current  | V <sub>IN</sub> = V <sub>CC</sub> or V <sub>SS</sub>                         |                       | 1                                    | μA   |

| I <sub>LO</sub>  | Output Leakage Current | V <sub>IN</sub> = V <sub>CC</sub> or V <sub>SS</sub>                         |                       | 1                                    | μA   |

| V <sub>IL</sub>  | Input LOW Voltage      | 1.65V <u>≤</u> V <sub>CC</sub> <u>≤</u> 2.7V                                 | -0.6 <sup>[9]</sup>   | 0.3 V <sub>CC</sub>                  | V    |

|                  |                        | 2.7V <u>&lt;</u> V <sub>CC</sub> <u>&lt;</u> 5.5V                            | -0.6 <sup>[9]</sup>   | 0.8                                  |      |

| V <sub>IH</sub>  | Input HIGH Voltage     | 1.65V <u>&lt;</u> V <sub>CC</sub> <u>&lt;</u> 5.5V                           | 0.7 V <sub>CC</sub>   | V <sub>CC</sub> + 0.5 <sup>[9]</sup> | V    |

| V <sub>OL</sub>  | Output LOW Voltage     | I <sub>OL</sub> = 2.1 mA, 2.7 <u>&lt;</u> V <sub>CC</sub> <u>&lt;</u> 5.5V   |                       | 0.4                                  | V    |

|                  |                        | I <sub>OL</sub> = 0.15 mA, 1.65 <u>&lt;</u> V <sub>CC</sub> <u>&lt;</u> 2.7V |                       | 0.2                                  |      |

| V <sub>OH</sub>  | Output HIGH Voltage    | I <sub>OH</sub> = -0.1 mA, 1.65 <u>&lt;</u> V <sub>CC</sub> ≤ 2.7V           | V <sub>CC</sub> - 0.2 |                                      | V    |

|                  |                        | $I_{OH}$ = -0.4 mA, 2.7 $\leq V_{CC} \leq 5.5V$                              | 2.4                   |                                      |      |

# Capacitance

In the following table, the capacitance parameters are listed. <sup>[10]</sup>

| Parameter        | Description            | Test Conditions                   | Max | Unit |

|------------------|------------------------|-----------------------------------|-----|------|

| C <sub>IN</sub>  | Input Capacitance      | T <sub>A</sub> = 25°C, f = 1 MHz, | 5   | pF   |

| C <sub>OUT</sub> | Output Pin Capacitance | V <sub>CC</sub> = 1.65V           | 5   | pF   |

## **Thermal Resistance**

In the following table, the thermal resistance parameters are listed. <sup>[10]</sup>

| Parameter     | Description                                 | Test Conditions                                                                                      | 8-SOIC | 8-TSSOP | Unit |

|---------------|---------------------------------------------|------------------------------------------------------------------------------------------------------|--------|---------|------|

| $\Theta_{JA}$ | Thermal Resistance<br>(Junction to Ambient) | Test conditions follow standard test methods and procedures for measuring thermal impedance, per EIA | 120.83 | 119.31  | °C/W |

| $\Theta_{JC}$ | Thermal Resistance<br>(Junction to Case)    | / JESD51.                                                                                            | 90.31  | 82.77   | °C/W |

#### Notes

8. Outputs shorted for only one second. Only one output shorted at a time.

9. This parameter is characterized but not tested.

10. This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

## **Reliability Characteristics**

In the following table, the reliability characteristics parameters are listed. <sup>[10]</sup>

| Parameter        | Description     | Test Method         | Min                   | Unit   |

|------------------|-----------------|---------------------|-----------------------|--------|

| N <sub>END</sub> | Endurance       | JEDEC Standard A117 | 1 Million             | Cycles |

| T <sub>DR</sub>  | Data Rentention | JEDEC Standard A103 | 100                   | Years  |

| I <sub>LTH</sub> | Latch Up        | JEDEC Standard 78   | 100 + I <sub>CC</sub> | mA     |

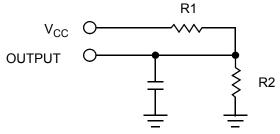

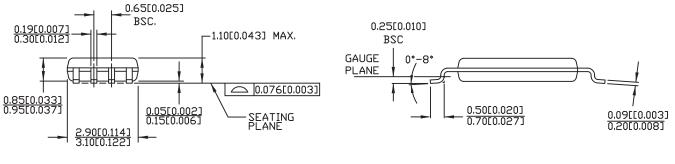

#### Figure 9. AC Test Loads and Waveforms

| Parameters | 1.65V - 2.7V | 2.7V - 5.5V | Unit |

|------------|--------------|-------------|------|

| R1         | 1.8K         | 1.8K        | ohm  |

| R2         | 1.3K         | 1.3K        | ohm  |

| CL         | 30           | 100         | pF   |

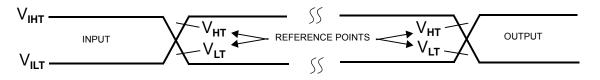

## Figure 10. AC Input/Output Reference Waveforms

AC test inputs are driven at  $V_{IHT}$  (0.9 $V_{CC}$ ) for a logic '1' and  $V_{ILT}$  (0.1 $V_{CC}$ ) for a logic '0'. Measurement reference points for inputs and outputs are  $V_{LT}$  ( $V_{CC}/2 - 0.1V$ ) and  $V_{HT}$  ( $V_{CC}/2 + 0.1V$ ). Input rise and fall times (10%–90%) are <3.3 ns.

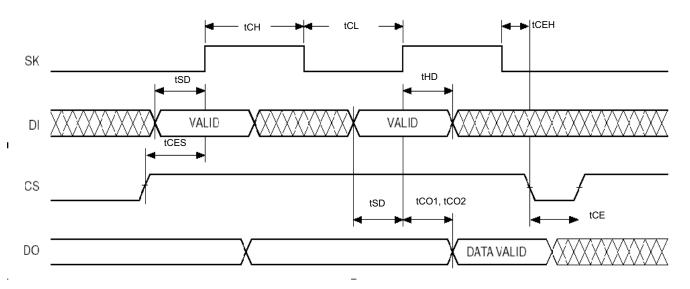

# **AC Switching Characteristics**

Over the Operating Range (V<sub>CC</sub>= 1.65V-5.5V)

| Cypress           | Alt<br>Parameter  | Description                      | 4 MHz |     | 3 Mhz |     | 2 Mhz |     | 1 Mhz |     | Unit |

|-------------------|-------------------|----------------------------------|-------|-----|-------|-----|-------|-----|-------|-----|------|

| Parameter         |                   | Description                      |       | Max | Min   | Max | Min   | Max | Min   | Max | Unit |

| f <sub>SK</sub>   | f <sub>SK</sub>   | Clock Frequency                  |       | 4   |       | 3   |       | 2   |       | 1   | MHz  |

| t <sub>CL</sub>   | t <sub>SKLO</sub> | Clock Pulse Width Low            | 100   |     | 130   |     | 200   |     | 400   |     | ns   |

| t <sub>CH</sub>   | t <sub>SKHI</sub> | Clock Pulse Width High           | 100   |     | 130   |     | 200   |     | 400   |     | ns   |

| t <sub>CE</sub>   | t <sub>CS</sub>   | Minimum CS Low Time              | 100   |     | 130   |     | 200   |     | 400   |     | ns   |

| t <sub>LZCE</sub> | t <sub>SV</sub>   | Output Valid                     |       | 100 |       | 130 |       | 200 |       | 400 | ns   |

| t <sub>CES</sub>  | t <sub>CSS</sub>  | CS Setup Time                    | 60    |     | 50    |     | 50    |     | 50    |     | ns   |

| t <sub>CEH</sub>  | t <sub>CSH</sub>  | CS Hold Time                     | 0     |     | 0     |     | 0     |     | 0     |     | ns   |

| t <sub>SD</sub>   | t <sub>DIS</sub>  | Data In Setup Time               | 60    |     | 50    |     | 100   |     | 100   |     | ns   |

| t <sub>HD</sub>   | t <sub>DIH</sub>  | Data In Hold Time                | 60    |     | 50    |     | 100   |     | 100   |     | ns   |

| t <sub>CO2</sub>  | t <sub>PD1</sub>  | Output Delay to 1                |       | 100 |       | 130 |       | 200 |       | 400 | ns   |

| t <sub>CO1</sub>  | t <sub>PD0</sub>  | Output Delay to 0                |       | 100 |       | 130 |       | 200 |       | 400 | ns   |

| t <sub>HZCE</sub> | t <sub>HZ</sub>   | CS to Data Out in High Impedance |       | 60  |       | 150 |       | 150 |       | 150 | ns   |

| t <sub>WC</sub>   | t <sub>WP</sub>   | Write Cycle Time                 |       | 5   |       | 5   |       | 5   |       | 5   | ms   |

| t <sub>F</sub>    | t <sub>F</sub>    | Input Fall Time                  |       | 20  |       | 28  |       | 45  |       | 95  | ns   |

| t <sub>R</sub>    | t <sub>R</sub>    | Input Rise Time                  |       | 20  |       | 28  |       | 45  |       | 95  | ns   |

## Figure 11. Synchronous Data Timing

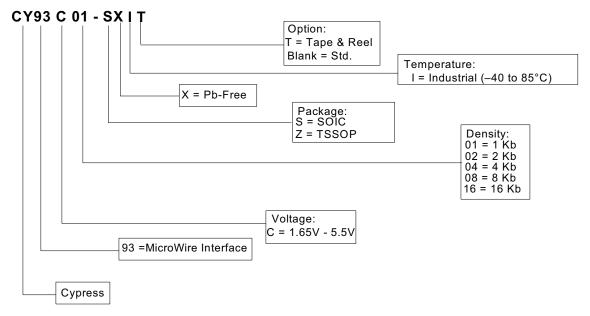

# Part Numbering Nomenclature

# **Ordering Information**

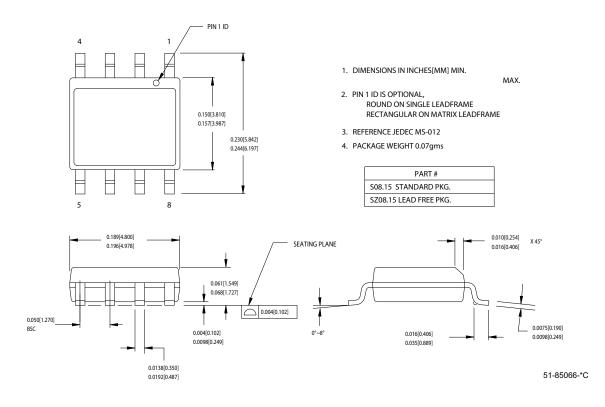

| Density | Ordering Code | Package<br>Diagram | Package Type              | Operating<br>Range |

|---------|---------------|--------------------|---------------------------|--------------------|

| 1 Kbit  | CY93C01-SXI   | 51-85066           | 8-Pin SOIC                | Industrial         |

|         | CY93C01-SXIT  |                    | 8-Pin SOIC (Tape & Reel)  | 1                  |

|         | CY93C01-ZXI   | 51-85093           | 8-Pin TSSOP               | -                  |

|         | CY93C01-ZXIT  |                    | 8-Pin TSSOP (Tape & Reel) | 1                  |

| 2 Kbit  | CY93C02-SXI   | 51-85066           | 8-Pin SOIC                | Industrial         |

|         | CY93C02-SXIT  |                    | 8-Pin SOIC (Tape & Reel)  |                    |

|         | CY93C02-ZXI   | 51-85093           | 8-Pin TSSOP               | _                  |

|         | CY93C02-ZXIT  |                    | 8-Pin TSSOP (Tape & Reel) |                    |

| 4 Kbit  | CY93C04-SXI   | 51-85066           | 8-Pin SOIC                | Industrial         |

|         | CY93C04-SXIT  |                    | 8-Pin SOIC (Tape & Reel)  |                    |

|         | CY93C04-ZXI   | 51-85093           | 8-Pin TSSOP               | -                  |

|         | CY93C04-ZXIT  |                    | 8-Pin TSSOP (Tape & Reel) |                    |

| 8 Kbit  | CY93C08-SXI   | 51-85066           | 8-Pin SOIC                | Industrial         |

|         | CY93C08-SXIT  |                    | 8-Pin SOIC (Tape & Reel)  |                    |

|         | CY93C08-ZXI   | 51-85093           | 8-Pin TSSOP               | -                  |

|         | CY93C08-ZXIT  |                    | 8-Pin TSSOP (Tape & Reel) |                    |

| 16 Kbit | CY93C16-SXI   | 51-85066           | 8-Pin SOIC                | Industrial         |

|         | CY93C16-SXIT  |                    | 8-Pin SOIC (Tape & Reel)  | 1                  |

|         | CY93C16-ZXI   | 51-85093           | 8-Pin TSSOP               |                    |

|         | CY93C16-ZXIT  |                    | 8-Pin TSSOP (Tape & Reel) | 1                  |

Above table contains Preliminary information. Please contact your local Cypress sales representative for availability of these parts.

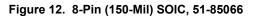

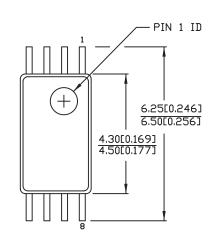

# **Package Diagrams**

## Package Diagrams (continued)

Figure 13. 8-Pin (4.4 mm) TSSOP, 51-85093

DIMENSIONS IN MMEINCHES] MIN. MAX.

REFERENCE JEDEC MD-153

| PART #   |                |  |  |  |  |  |

|----------|----------------|--|--|--|--|--|

| Z08.173  | STANDARD PKG.  |  |  |  |  |  |

| ZZ08.173 | LEAD FREE PKG. |  |  |  |  |  |

51-85093-\*A

# **Document History Page**

# Document Title: CY93C01/02/04/08/16, 1 Kbit, 2 Kbit, 4 Kbit, 8 Kbit, and 16 Kbit (x8 or x16) MicroWire Serial EEPROM Document Number: 001-15635

| Revision | ECN No. | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | 1069220 | UHA                | See ECN            | New Data Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| *A       | 2522135 | GVCH/PYRS          | 06/27/08           | Added Pb-Free and RoHS Compliant information in Features<br>Removed PDIP package<br>Removed Automotive Temperature range<br>Changed Supply voltage on $V_{CC}$ relative to GND max value from 5.0V to<br>6.0V<br>Corrected Typo of Vcc max value from 5.0V to 5.5V<br>Added AC test load values for different parameters<br>Table 10: Updated AC Switching Characteristics<br>Table 8: Added Thermal Resistance values for 8-TSSOP packages<br>Table 9: Changed T <sub>DR</sub> value from 20 to 100 years<br>Updated Part Numbering Nomenclature and Ordering Information                                                                                                                                                                                                                                                                                    |

| *В       | 2611873 | VKN/PYRS           | 11/24/08           | Updated Part numbering nomenclature<br>Updated Ordering information table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| *C       | 2656511 | VKN/AESA           | 02/09/09           | $\begin{array}{l} \label{eq:converted} \mbox{CY93C46/56/66/76/86 to CY93C01/02/04/08/16} \\ \mbox{Converted from preliminary to final} \\ \mbox{Included V}_{IL} \mbox{ spec of } 0.8V \mbox{ for the V}_{CC} \mbox{ range between } 2.7V \mbox{ to } 5.5V \\ \mbox{Updated V}_{IH} \mbox{ test conditions} \\ \mbox{Added footnote } \#9 \\ \mbox{Updated V}_{OL} \mbox{ and V}_{OH} \mbox{ test conditions} \\ \mbox{On page 10, Specified V}_{CC} \mbox{ range for AC test load conditions} \\ \mbox{On page 10, corrected AC measurement reference points from V}_{IT} \mbox{ and V}_{OT} \mbox{ to V}_{LT} \mbox{ and V}_{HT} \mbox{ respectively} \\ \mbox{Changed V}_{LT} \mbox{ level from } 0.3V_{CC} \mbox{ to V}_{CC}/2 \mbox{ - } 0.1V \\ \mbox{Changed V}_{HT} \mbox{ level from } 0.7V_{CC} \mbox{ to V}_{CC}/2 \mbox{ + } 0.1V \\ \end{array}$ |

## Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at cypress.com/sales.

| Products         |                      | <b>PSoC Solutions</b> |                                   |

|------------------|----------------------|-----------------------|-----------------------------------|

| PSoC             | psoc.cypress.com     | General               | psoc.cypress.com/solutions        |

| Clocks & Buffers | clocks.cypress.com   | Low Power/Low Voltage | psoc.cypress.com/low-power        |

| Wireless         | wireless.cypress.com | Precision Analog      | psoc.cypress.com/precision-analog |

| Memories         | memory.cypress.com   | LCD Drive             | psoc.cypress.com/lcd-drive        |

| Image Sensors    | image.cypress.com    | CAN 2.0b              | psoc.cypress.com/can              |

|                  |                      | USB                   | psoc.cypress.com/usb              |

© Cypress Semiconductor Corporation, 2007-2009. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document #: 001-15635 Rev. \*C

#### Revised February 05, 2009

Page 16 of 16

All products and company names mentioned in this document may be the trademarks of their respective holders.